2023.2.2에 생일이라서 2.3~2.5 까지 강릉여행, 1.30, 1.31, 2.1 출근

2023.1.30 ( 월 )

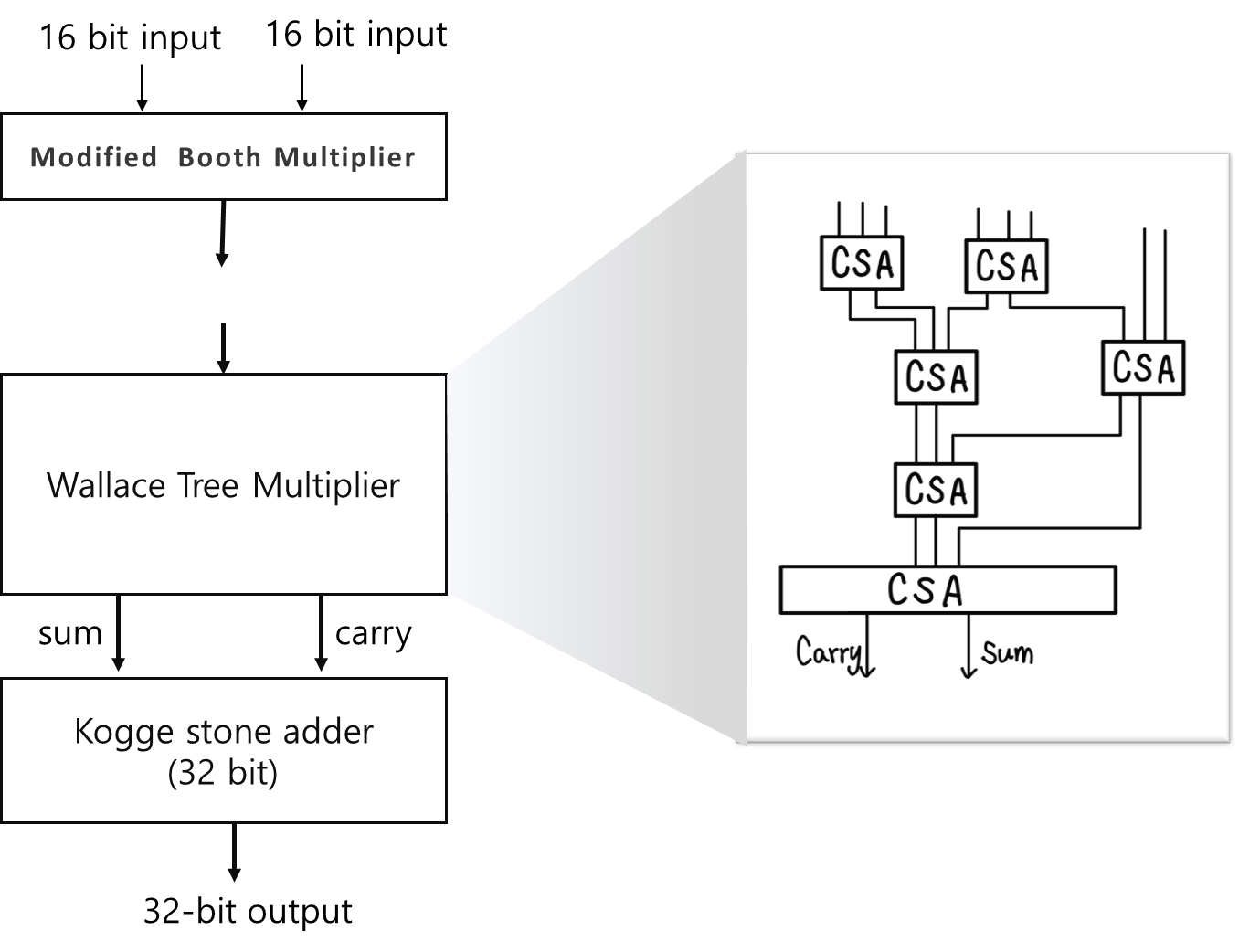

| New Project : Wallace Tree Multiplier을 통한 16 bit x 16bit 멀티플라이어 만들기, Kogge Stone Adder |

| 1. 16bit signed number x 16bit signed number이 가능한 Wallace Tree Multiplier 조사하기 2. gate level 구현할 계획. 사용할 프로그램은 Virtuoso (Schematic Level) 3. multiplier 구조는 wallace tree multiplier 4. adder : Kogge Stone Adder |

wallace tree multiplier 자료

논문정리 - 8bit 곱셈기 설계

논문정리 - 32bit 곱셈기 설계

16x 16 bit Multiplier 고안

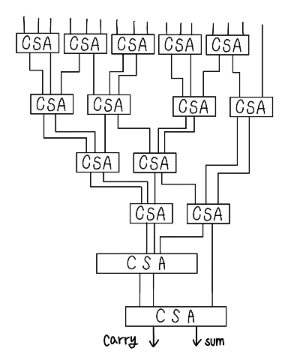

Wallace Tree Multiplier

16-bit이기에 booth 알고리즘을 사용하기 애매했으나 위와같은 회로도가 짜이자 booth알고리즘을 가능하면 적용하기로 하였다. booth 알고리즘을 사용하기 애매한 이유는 한 모듈 안에 두개의 알고리즘이 들어가면 면적을 많이 차지하기에 속도 효율이 더 안좋아 지기 때문이다. 한 모듈 안에 여러 알고리즘을 넣어 속도를 향상시키는 것은 32bit 이상과 같은 큰 bit에서 더 효율적이다.

미팅

booth 알고리즘 이해하기 위에 붙이기

sigend, unsigned 멀리플라이어 이해하기

2023.1.31 ( 화 )

개념: Unsigned Multiplier

Partial product의 계산 방법에 따라 adder가 달라진다.

Ripple Carry Adder 사용

Carry의 전파가 옆으로 발생하여 매 덧셈마다 생기므로 불합리하다.

Carry Save Adder 사용

•Carry의 전파가 아래로 (다음 단)으로 발생하여 다음 단의 partial product와의 덧셈

•옆에서 전파되는 carry를 기다리지 않음

•최종단에서는 모든걸 더한 값으로 ripple carry을 피할 수 없음. 따라서 마지막단에는 다른 carry를 옆으로 전파하는 adder을 사용해야한다.

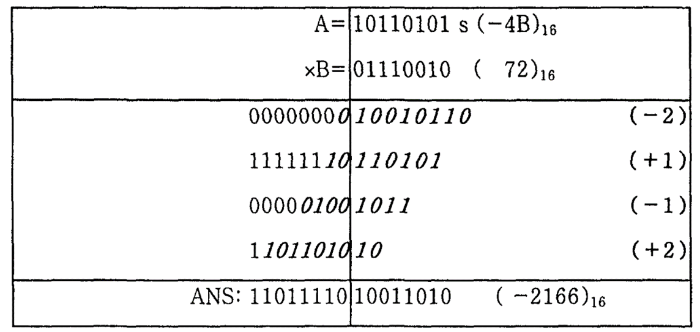

개념: signed Multiplier

| 2진 곱셈 시 주의 할 점 |

|

• 양수와 음수의 곱인데 결과가 양수 → (1) 부호확장하기

• 음수와 음수의 곱인데 결과가 음수 → (2) signed bit과 곱해진 partial product는 2의 보수를 취하기

|

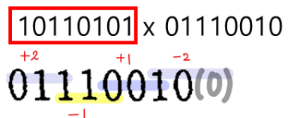

개념: Modified Booth Multiplier

①3bit 씩 묶은 뒤 y recoding을 통해 값을 넣는다.

②다음 단으로 갈때마다 2 bit씩 건넌다.

③모두 마치면 모든 단을 합친다.

짝수가 중앙값을 차지하여 곱셈 계수가 홀수 차수만 갖도록 변환한다. Ex) 2^(-2)=2^(-1)-2^1 x 2^(-3)

| Y_2i+1 | y_2i | y_2i-1 | Y_i ‘ | X_sel | 2x_sel | Neg |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 2 | 0 | 1 | 0 |

| 1 | 0 | 0 | -2 | 0 | 1 | 1 |

| 1 | 0 | 1 | -2 | 1 | 0 | 1 |

| 1 | 1 | 0 | -1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 1 |

•Y_i’ = 0인 경우 그 행은 0의 값을 가진다.

•Y_i가 음수인 경우는 위와 마찬가지의 방법에 보수를 취하면 된다.

•NEG는 부호전환으로 1인 경우 부호를 전환한다.

Example 8bit x 8 bix

∴결과

8bit x 8bitx의 partial product 가 8개가 아닌 4개로 절반이 줄었다.

따라서 이를 모두 더하는 adder의 수가 줄음을 확인할 수 있다.

Multiplier 구상

2023.2.1 ( 수 )

개념 : Kogge stone adder

•Kogge stone adder은 CLA를 단계로 나눠 각 단계에서 병렬 연산을 하는 CLA 형태의 prefixe adder이다.

•따라서 KSA에서도 P,G개념을 갖는다. (G는 캐리를 만드는 것이며 P는 하위 bit carry를 상위 bit로 전달해주는것이다.)

[참고 문헌]

- 서경진 , 김평,이윤호 (2017) , “완전동형암호로 암호화된 데이터에 적합한 산술 가산기의 구현 및 성능향상에 관한 연구 “ , 서울과학기술대학교, Journal of The Korea Institute of Information Security & Cryptology VOL.27, NO.3 ,page 417-2.2.1

- 김홍욱 ( 1996 ) ” 0.8um CMOS 공정을 이용한 32x32 bit paraller multiplier 설계” . 단국대학교 대학원. 석사학위 논문.569.8

- “Multiplier Structur”, 한국기술교육대학교 전기전자통신공학부

'multiplier, adder 연구일지' 카테고리의 다른 글

| 16x16 Praller Signed Multiplier (1) | 2023.05.09 |

|---|---|

| 32bit-Brent Kung-Adder (0) | 2023.03.09 |

| 9주차 (2023.02.20~2023.02.26) 32bit KSA , Final Simulaion (0) | 2023.02.24 |

| 8주차 (2023. 02.15~2023.02.17) Booth Algorithm, Wallace Tree (0) | 2023.02.22 |

| 7주차 ( 2023.02.06~2023.02.09 ) (0) | 2023.02.06 |