2023.01.04 (수)

10:00~18:00

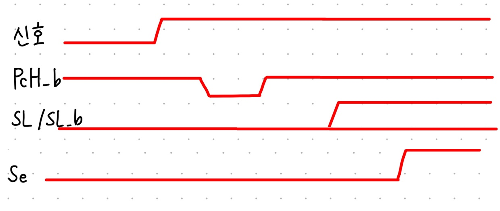

| 설계할 신호 |

| 신호가 들어오면 PcH_b가 5ns 뒤에 5ns 동안 0이 된다. 신호가 들어오고 10ns 뒤에 SL이 1이 되고 지속된다. 신호가 들어오고 15ns 뒤에 Se 신호가 1이 되고 지속된다. |

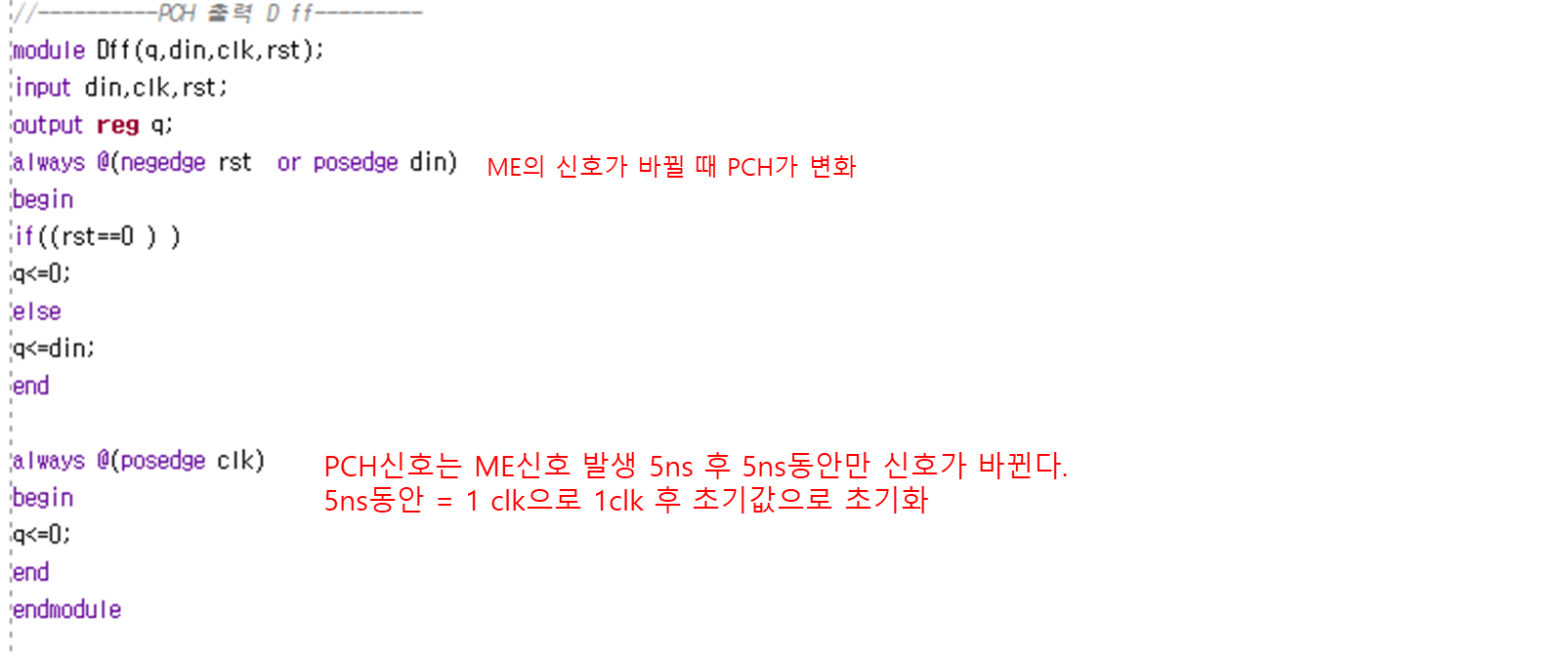

PCH_b 신호

- Initial 신호가 1, me신호가 0->1이 될 때 5ns 이후에 5ns 동안 신호 변화

- PCH 신호용 Dff 설계하기.

- 입력신호가 posedge 일 때 PcH 신호 발생

- Clock을 사용하여 5ns 동아 신호 발생 후 Initial 신호로 초기화

- PCH신호에 not gate를 연결하여 PCH_b 신호 생성

SL,SE 신호

SE신호는 SL신호가 right shift 된것이므로 D FF를 연결하여 right shift 해준다.

또한 SL,SE신호는 각각 negedge clk, posedge clk으로 신호를 받았으며 그 이유는 그 신호 사이 간격이 5ns로 만들어 주기 위함이다.

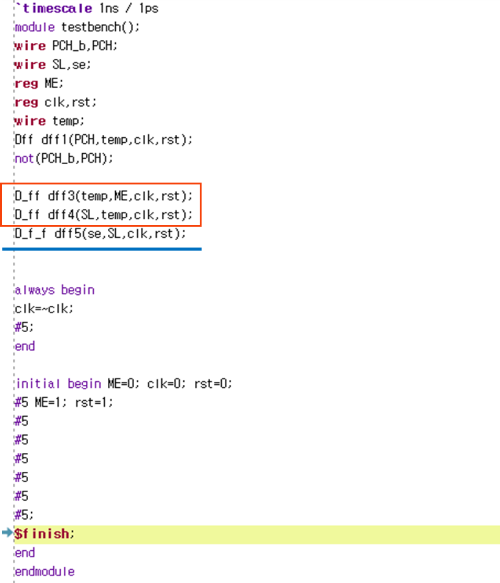

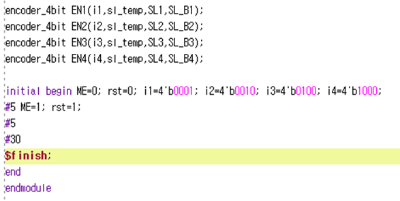

TESTBENCH

Simulation

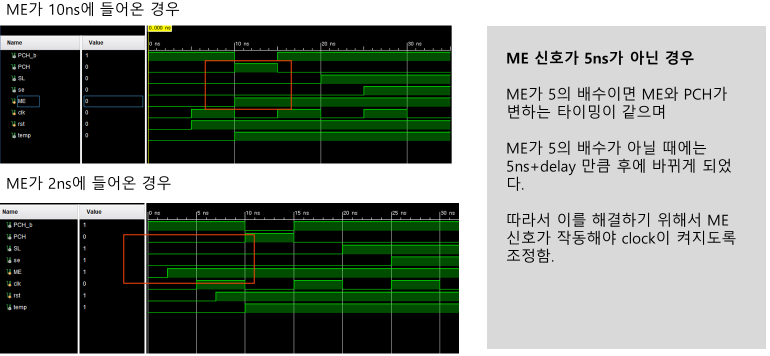

분석

Forever 구문

forever구문은 $finish를 만나면 멈추는 구문이다.

입력신호가 posedge일때 클락을 발생시켜 신호들이 5ns 간격으로 신호가 정상작동하게 만들 수 있다.

clk이 ME(입력신호)가 변화가 생길 때 작동한다. 그전까지는 작동을 안함.

궁금점

- 일단 주어진 대로 시뮬레이션을 만들었으나 어떻게 작동하는 것인지 원리를 잘 몰라 표면적으로만 시뮬레이션이 나오게 작업을 하였다. 따라서 BNN, ferarm 신호 설계에 대한 공부가 필요해 보인다.

=> 더 생각해보고 알려주신다고 함. 금요일에 선배가 하는 feram 디지털설계 설명을 들을 예정

- SL_B신호는 아직 설계하지 않았는데, SL / SL_B신호는 SL_B는 0이고 SL은 입력신호에 따라 변화한다. 특정할 때에는 그 반대의 상황도 가능하며 이것 또한 이 과제에 포함해야 하는데 감지 잡히지 않는다.

=> SL은 ME의 신호가 아닌 외부 변수 신호를 받아야 한다.

=> 00 01 10 11 의 경우를 생각해야 하므로 4bit의 신호를 받는다.

- 일반적인 컴퓨터에서 코딩은 코드를 작성하면 코드가 CPP파일에서 obj파일로 처리되고 다음으로 exe파일이 되어 메모리에 들어간다. 그렇다면 verilog도 모듈을 작성하고 실행하면 위와 같은 과정을 통해 메모리에 들어가 실행이 되는 것일까? 처리과정에 대해 궁금하다.

=> 소프트웨어와 하드웨어 체계는 다르다. 우리가 하는 verilog와 c++같이 컴퓨터에 출력되는것은 같은 원리지만 실제로 하드웨어에 입력해서 모듈을 설정하고 하는것은 FPGA를 사용하여 외부입력으로 나간다.

| Next 과제 |

| SL신호를 빼고는 건드릴게 없다 (야호) PCH, SE신호는 ME신호를 받는게 맞지만 SL신호는 아니다. 따라서 SL신호를 다시 설정해야 하는데 SL신호는 외부 변수를 따로 입력받아야 한다. 초기값은 모두 0으로 설정하지만 타이밍만 같이 받는다. 즉 입력신호는 다르지만 PCH가 반응하고 다음 5ns에서 다음과 같이 신호가 변화해야한다. SL[x] 에서 x는 외부변수이다. SL_in[0] : SL=1 , SL_B=0 SL_in[1] : SL=0, SL_B=0 SL_in[2] : SL=1, SL_B=1 SL_in[3] : SL=0, SL_B=1 |

2023.01.06 (금)

10:00 ~ 18:00 이전 과제의 연장선

SL, SL_B 신호

주어진 과제의 입력은 4bit으로 신호 변화는 SL,SL_B가 00 01 10 11로 4가지 출력이 있다. 입력이 4bit인데 출력은 1bit으로 4개의 출력값을 골라야 한다. 즉 입력은 4bit이지만 상태는 4가지가 나와야 한다.

따라서 16 (2^4) to 4 encoder을 만들었다.

| input | SL | SL_B |

| 0 0 0 1 | 0 | 0 |

| 0 0 1 0 | 0 | 1 |

| 0 1 0 0 | 1 | 0 |

| 1 0 0 0 | 1 | 1 |

SL,SL_B에 대해 각각 temp을 설정하고 SL,SL_B에서 쓰지 않는 신호는 x 처리 한다.

timing을 받아 timing이 변화 할 때 SL,SL_B가 입력되고 그 외에는 0이 출력된다.

모든 값이 잘 출력되는 지 확인하기 위해 4개의 encoder을 만들고 각각의 숫자를 넣어 testbench를 해봤다.

원하는 신호로 출력되었다. 야호~

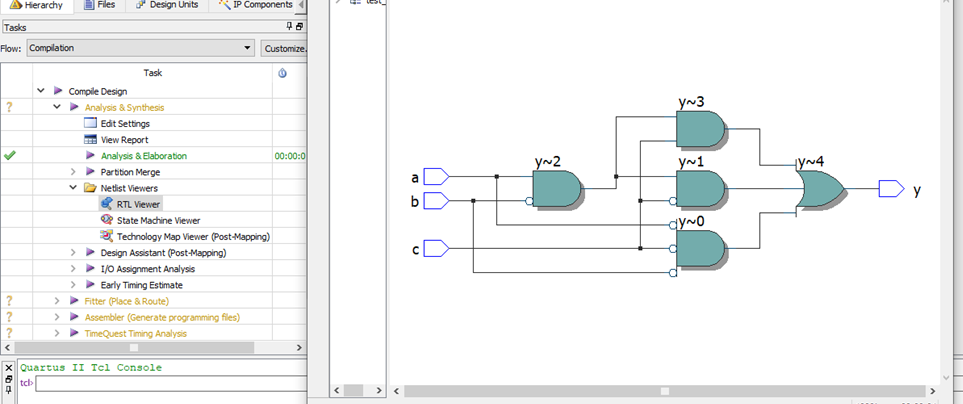

Self study

쿼터스2 13.1 RTL 뷰어

module test_1(input a,b,c,output y);

assign y=~a& ~b&~c|a& ~b&~c|a& ~b&c;

endmodule

집가고싶다

'feram control signal 연구일지' 카테고리의 다른 글

| 5주차 ( 2023.01.23~2023.01.27 ) FPGA 연결 (0) | 2023.01.27 |

|---|---|

| 4주차 ( 2023.01.16~2023.01.20 ) FeRam Contorl 신호 베릴로그 (0) | 2023.01.13 |

| 3주차 ( 2023.01.09~2023.01.13 ) (0) | 2023.01.11 |

| 1주차 (2022.12.26~ 12.30) (0) | 2022.12.28 |