1. 2023.01.25 ( 수 )

쿼터스로 베릴로그 재작성

시뮬레이션 돌리기

module dd(clk,clk_pch,rst,me,pch,sl_in,sl0,sl_b0,sl1,sl_b1,sl2,sl_b2,sl3,sl_b3,timing,sl_temp,sl_b_temp,sl,sl_b,wl,se);

input clk,rst,me,clk_pch;

output pch,sl,wl,se;

input [0:3] sl_in;

output reg sl0,sl_b0,sl1,sl_b1,sl2,sl_b2,sl3,sl_b3;

input timing,sl_temp,sl_b_temp;

output reg sl_b;

endmodule

//----------negedge clk D ff ---------

module negedge_Dff(q,din,clk,rst);

input din,clk,rst;

output reg q;

always @(negedge rst or negedge clk) begin

if(rst==0 )

q<=0;

else

q<=din; end

endmodule

//----------posedge clk D ff---------

module posedge_Dff(q,din,clk,rst);

input din,clk,rst;

output reg q;

always @(negedge rst or posedge clk) begin

if(rst==0 )

q<=0;

else

q<=din;

end

endmodule

//------------------SL 신호-----------------

module SL_signal(SL_in,S0,S1,S2,S3,S_B0,S_B1,S_B2,S_B3);

input [0:3] SL_in;

output reg S0,S1,S2,S3,S_B0,S_B1,S_B2,S_B3;

always @(SL_in) begin

if (SL_in[0]==1) S0=0;

else if(SL_in[0]==0) S0=1;

if (SL_in[1]==1) S1=0;

else if(SL_in[1]==0) S1=1;

if (SL_in[2]==1) S2=0;

else if(SL_in[2]==0) S2=1;

if (SL_in[3]==1) S3=0;

else if(SL_in[3]==0) S3=1;

S_B0= ~S0; S_B1= ~S1; S_B2= ~S2; S_B3= ~S3; end

endmodule

module SL_output(timing,SL_temp,SL_B_temp, SL,SL_B);

input timing,SL_temp,SL_B_temp;

output reg SL,SL_B;

always@(timing) begin

if(timing==1) begin

SL=SL_temp;

SL_B=SL_B_temp; end

else begin

SL=0;

SL_B=0; end

end

endmodule

module PCH(x,z,clk,rst);

input x,clk,rst;

output z;

wire d1,d2,d22,q2_not,q1,q2,q1_not;

//q1,q2 q1'q2'

not(q2_not,q2);

not(q1_not,q1);

//d1 gate 연결

or(d1,q1,q2);

//d2 gate 연결

and(d2,x,q2_not);

or(d22,d2,q1);

//z gate연결

and(z,q1_not,q2);

negedge_Dff dff1(q1,d1,clk,rst);

negedge_Dff dff2(.q(q2),.din(d22),.clk(clk),.rst(rst));

endmodulemodule testbench();

reg clk,rst,ME;

reg PCH_clk;

wire PCH,PCH_b;

PCH PCH_signal(ME,PCH,clk,rst);

not(PCH_b,PCH);

always begin

PCH_clk=~PCH_clk;

#2.5;

end

always begin

clk=~clk;

#5;

end

//negedge_Dff dff1(PCH,ME,clk,rst);

//not(PCH_b,PCH);

wire sl_timing,sl_timing_temp,se;

reg [0:3] SL_in;

negedge_Dff sl_temp1(sl_timing_temp,ME,clk,rst);

negedge_Dff sl_temp2(sl_timing,sl_timing_temp,clk,rst);

posedge_Dff se_siganl(se,sl_timing,clk,rst);

wire SL0_temp,SL1_temp,SL2_temp,SL3_temp,SL_B0_temp,SL_B1_temp,SL_B2_temp,SL_B3_temp;

wire SL0,SL1,SL2,SL3,SL_B0,SL_B1,SL_B2,SL_B3;

SL_signal SL_siganl(SL_in,SL0_temp,SL1_temp,SL2_temp,SL3_temp,SL_B0_temp,SL_B1_temp,SL_B2_temp,SL_B3_temp);

SL_output SL_output0(sl_timing,SL0_temp,SL_B0_temp,SL0,SL_B0);

SL_output SL_output1(sl_timing,SL1_temp,SL_B1_temp,SL1,SL_B1);

SL_output SL_output2(sl_timing,SL2_temp,SL_B2_temp,SL2,SL_B2);

SL_output SL_output3(sl_timing,SL3_temp,SL_B3_temp,SL3,SL_B3);

initial begin ME=0; rst=0; SL_in=4'b0011; clk=0;PCH_clk=0;

// i1=4'b0001; i2=4'b0010; i3=4'b0100; i4=4'b1000;

#5 ME=1; rst=1;

#35

$finish;

end

endmodule

2. 2023.01.27 ( 금 )

2.1. 코드수정

`timescale 1ns / 1ps

module feram(clk,clk_pch,rst,ME,pch,pch_b,SL_in,SL0,SL1,SL2,SL3,SL_B0,SL_B1,SL_B2,SL_B3,sl_timing,se);

input clk,rst,ME,clk_pch;

output pch,pch_b,se,sl_timing;

input [0:3] SL_in;

output SL0,SL_B0,SL1,SL_B1,SL2,SL_B2,SL3,SL_B3;

wire pch,pchtemp;

wire pch_b;

//negedge_Dff PCHDFF(pchtemp,ME,clk,rst);

wire pchtemp1,me_not;

not(me_not,ME);

PCH PCH_signal(ME,pch,clk,rst);

//and(pch,clk,me_not);

not(pch_b,pch);

wire SL0_temp,SL1_temp,SL2_temp,SL3_temp,SL_B0_temp,SL_B1_temp,SL_B2_temp,SL_B3_temp;

wire sl_timing_temp;

negedge_Dff sl_temp1(sl_timing_temp,ME,clk,rst);

posedge_Dff sl_temp2(sl_timing,sl_timing_temp,clk,rst);

negedge_Dff se_siganl(se,sl_timing,clk,rst);

SL_signal SL_siganl(SL_in,SL0_temp,SL1_temp,SL2_temp,SL3_temp,SL_B0_temp,SL_B1_temp,SL_B2_temp,SL_B3_temp);

SL_output SL_output0(sl_timing,SL0_temp,SL_B0_temp,SL0,SL_B0);

SL_output SL_output1(sl_timing,SL1_temp,SL_B1_temp,SL1,SL_B1);

SL_output SL_output2(sl_timing,SL2_temp,SL_B2_temp,SL2,SL_B2);

SL_output SL_output3(sl_timing,SL3_temp,SL_B3_temp,SL3,SL_B3);

endmodule

//----------negedge clk D ff ---------

module negedge_Dff(q,din,clk,rst);

input din,clk,rst;

output reg q;

always @(negedge rst or negedge clk) begin

if(rst==0 )

q<=0;

else

q<=din; end

endmodule

//----------posedge clk D ff---------

module posedge_Dff(q,din,clk,rst);

input din,clk,rst;

output reg q;

always @(negedge rst or posedge clk) begin

if(rst==0 )

q<=0;

else

q<=din;

end

endmodule

//------------------SL 신호-----------------

module SL_signal(SL_in,S0,S1,S2,S3,S_B0,S_B1,S_B2,S_B3);

input [0:3] SL_in;

output reg S0,S1,S2,S3,S_B0,S_B1,S_B2,S_B3;

always @(SL_in) begin

if (SL_in[0]==1) S0=0;

else if(SL_in[0]==0) S0=1;

if (SL_in[1]==1) S1=0;

else if(SL_in[1]==0) S1=1;

if (SL_in[2]==1) S2=0;

else if(SL_in[2]==0) S2=1;

if (SL_in[3]==1) S3=0;

else if(SL_in[3]==0) S3=1;

S_B0= ~S0; S_B1= ~S1; S_B2= ~S2; S_B3= ~S3; end

endmodule

module SL_output(timing,SL_temp,SL_B_temp, SL,SL_B);

input timing,SL_temp,SL_B_temp;

output reg SL,SL_B;

always@(timing) begin

if(timing==1) begin

SL=SL_temp;

SL_B=SL_B_temp; end

else begin

SL=0;

SL_B=0; end

end

endmodule

module PCH(x,z,clk,rst);

input x,clk,rst;

output z;

wire d1,d2,d22,q2_not,q1,q2,q1_not;

//q1,q2 q1'q2'

not(q2_not,q2);

not(q1_not,q1);

//d1 gate 연결

or(d1,q1,q2);

//d2 gate 연결

and(d2,x,q2_not);

or(d22,d2,q1);

//z gate연결

and(z,q1_not,q2);

negedge_Dff dff1(q1,d1,clk,rst);

negedge_Dff dff2(.q(q2),.din(d22),.clk(clk),.rst(rst));

endmodule`timescale 1ns / 1ps

module testbench();

reg clk,rst,ME,PCH_clk;

wire pch,PCH_b,sl_timing,se;

reg [0:3] SL_in;

wire SL0,SL1,SL2,SL3,SL_B0,SL_B1,SL_B2,SL_B3;

always @(posedge ME) begin

clk=1;

forever #5 clk=~clk;

end

always @(posedge ME) begin

PCH_clk=1;

forever #2.5 PCH_clk=~PCH_clk;

end

feram feram1(clk,PCH_clk,rst,ME,pch,PCH_b,SL_in,SL0,SL1,SL2,SL3,SL_B0,SL_B1,SL_B2,SL_B3,sl_timing,se);

initial begin ME=0; rst=0; SL_in=4'b0011; clk=0;PCH_clk=0;

// i1=4'b0001; i2=4'b0010; i3=4'b0100; i4=4'b1000;

#5 ME=1; rst=1;

#35

$finish;

end

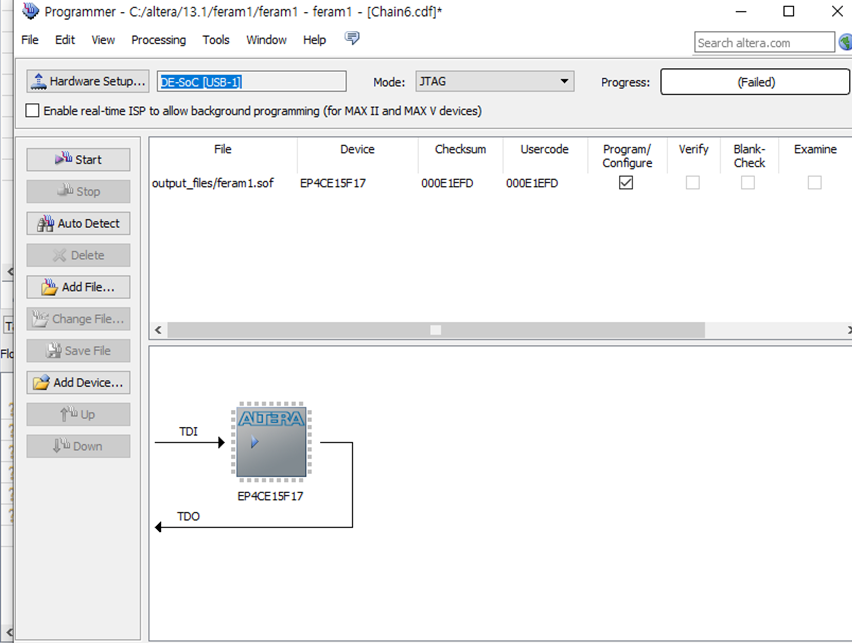

endmodule2.2. 쿼터스 연결

연결완 !

2.3. FPGA 연결

'feram control signal 연구일지' 카테고리의 다른 글

| 4주차 ( 2023.01.16~2023.01.20 ) FeRam Contorl 신호 베릴로그 (0) | 2023.01.13 |

|---|---|

| 3주차 ( 2023.01.09~2023.01.13 ) (0) | 2023.01.11 |

| 2주차 (2023.01.02~01.6) (0) | 2023.01.04 |

| 1주차 (2022.12.26~ 12.30) (0) | 2022.12.28 |